基于100G PAM4技术的LinkX线缆及其在计算机软硬件研发中的关键角色

随着数据中心、高性能计算和人工智能应用对数据传输速率要求的爆炸式增长,传统非归零码(NRZ)技术在高带宽需求面前已显乏力。在这一背景下,基于四级脉冲幅度调制(PAM4)技术的100G LinkX线缆应运而生,成为下一代高速互连的关键物理层解决方案,并深刻影响着计算机软硬件的研发方向。

一、PAM4技术与100G LinkX线缆的技术核心

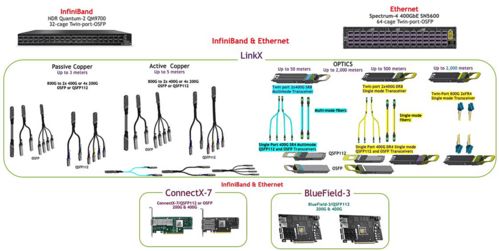

PAM4技术是一种先进的信号调制方式,它允许每个符号周期传输2比特信息(四种电平),相较于NRZ技术每个符号仅传输1比特信息,在相同带宽下有效将数据速率提升了一倍。100G LinkX线缆正是利用这一原理,在有限的物理通道(如铜缆或光纤)上实现100Gbps甚至更高的传输速率。这类线缆通常指有源电缆(AEC),集成了信号调理芯片(如重定时器Retimer或重驱动器Redriver),能够有效补偿信号在传输过程中的衰减和失真,从而支持更长的传输距离和更高的信号完整性。

二、对硬件研发的驱动与挑战

- 高速接口芯片设计:硬件研发的核心在于支持PAM4信号的专用集成电路(ASIC)和物理层(PHY)芯片。这要求芯片设计必须处理更复杂的信号调制、更严格的时序容限以及更高的功耗管理挑战。SerDes(串行器/解串器)设计需升级以支持PAM4信令,包括高性能模数/数模转换器、自适应均衡器和前向纠错(FEC)模块。

- PCB与连接器设计:主板、网卡、交换机的印刷电路板(PCB)设计必须应对更高速率带来的信号完整性挑战。需要采用更先进的材料(如低损耗介质)、更精密的布线规则(如阻抗控制、串扰抑制)以及支持更高频率的连接器(如QSFP-DD, OSFP)。

- 系统集成与测试:将支持100G PAM4的LinkX线缆集成到服务器、交换机、存储阵列中,需要全新的系统级验证和测试方法。研发重点包括通道仿真、眼图测试、误码率(BER)测试以及热插拔和互操作性测试,确保在真实环境中的稳定可靠。

三、对软件研发的影响与协同

- 驱动与固件开发:硬件功能的发挥离不开底层软件的支持。需要开发或升级网络接口卡(NIC)、交换芯片的驱动程序、固件(Firmware)和底层管理软件,以实现对PAM4链路的管理、状态监控(如信号质量、温度)、错误诊断和动态配置(如速率协商、功耗调整)。

- 网络协议栈优化:在应用层,更高的物理带宽要求网络协议栈(如TCP/IP)能够高效利用链路,避免成为瓶颈。软件研发需关注零拷贝技术、内核旁路(如DPDK、RDMA)、拥塞控制算法优化等,以降低延迟、提升吞吐量,充分发挥100G链路的潜力。

- 管理与编排软件:在大规模数据中心,成千上万条100G链路需要集中管理。软件研发需增强网络管理平台、遥测系统和自动化编排工具(如基于SONiC的网络操作系统),实现对高速链路的智能配置、性能监控、故障预测和自动化修复。

四、未来趋势与研发展望

基于100G PAM4的LinkX线缆技术正向200G、400G乃至800G演进。未来的研发将更加聚焦于:

- 共封装光学(CPO):将光引擎与交换芯片更紧密集成,进一步降低功耗和延迟。

- 硅光子学集成:利用硅工艺制造光学元件,实现光电集成芯片,降低成本与体积。

- 智能无损网络:通过软硬件协同,在RoCEv2等协议下构建完全无损的数据中心网络,满足AI/HP计算需求。

- 安全性增强:在物理层和数据链路层集成新的安全特性,防止窃听和篡改。

100G PAM4 LinkX线缆不仅是高速连接的“血管”,更是驱动计算机软硬件协同创新、向下一代数据中心架构演进的催化剂。其研发是一个涵盖材料科学、芯片设计、信号处理、系统集成和软件优化的跨学科系统工程,将持续引领计算与通信基础设施的深刻变革。

如若转载,请注明出处:http://www.xuqiuhezi.com/product/67.html

更新时间:2026-04-16 21:52:51